#### 香港中文大學 The Chinese University of Hong Kong

CENG3430 Rapid Prototyping of Digital Systems

## Lecture 03:

# **Combinational Circuit and Sequential Circuit**

**Ming-Chang YANG**

#### What we have learnt so far

- Combinational Circuit: no memory

- Outputs depend on the present inputs only.

- As soon as inputs change, the values of previous outputs are lost.

```

entity lab0 is

port (

A: in std_logic;

B: in std_logic;

C: out std_logic

);

end lab0;

architecture behavioral of lab0 is

begin

C <= A AND B;

end behavioral;</pre>

```

#### **Outline**

- Combinational Circuit: no memory

- Outputs depend on the *present* inputs only.

- Rule: Use either concurrent or sequential statements.

- Sequential Circuit: has memory

- Outputs depend on present inputs and previous outputs.

- Rule: MUST use sequential statements (i.e., process).

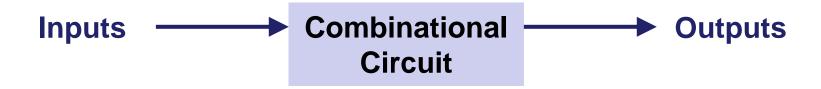

#### **Combinational Circuit**

- Combinational Circuit: no memory

- Outputs depend on the *present* inputs only.

- As soon as inputs change, the values of previous outputs are lost.

- Rule: You can build a combinational circuit using <u>either</u>

<u>concurrent statements</u> (i.e., <u>statements outside process</u>)

<u>or sequential statements</u> (i.e., <u>statements inside process</u>).

# **Modeling Combinational Circuit (1/3)**

- Typical ways for modeling a combinational circuit:

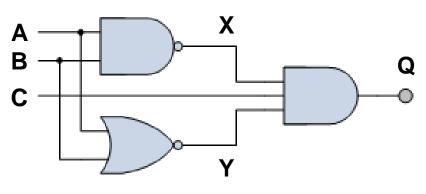

- 1) Logic/Schematic Diagram shows the wiring and connections of each individual logic gate.

- 2) Boolean Expression is an expression in Boolean algebra that represents the logic circuit.

- 3) Truth Table provides a concise list that shows all the output states for each possible combination of inputs

#### **Logic/Schematic Diagram**

```

architecture com_arch of comb is

signal X, Y: std_logic;

begin

X <= not (A and B);

Y <= not (A or B);

Q <= (X and C) and Y;

end com arch;</pre>

```

https://www.electronics-tutorials.ws/combination/comb\_1.html

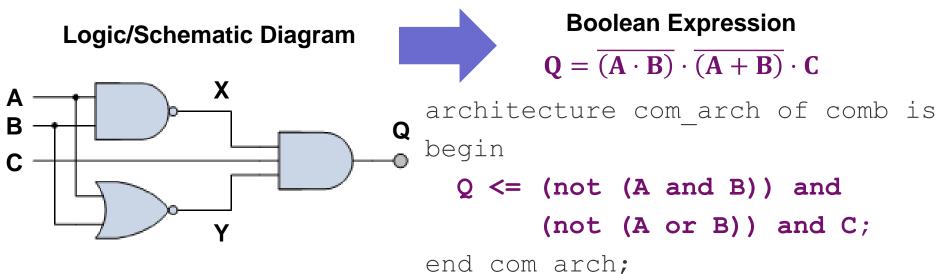

## **Modeling Combinational Circuit (2/3)**

- Typical ways for modeling a combinational circuit:

- 1) Logic/Schematic Diagram shows the wiring and connections of each individual logic gate.

- 2) Boolean Expression is an expression in Boolean algebra that represents the logic circuit.

- 3) Truth Table provides a concise list that shows all the output states for each possible combination of inputs

https://www.electronics-tutorials.ws/combination/comb\_1.html

# Modeling Combinational Circuit (3/3)

- Typical ways for modeling a combinational circuit:

- 1) Logic/Schematic Diagram shows the wiring and connections of each individual logic gate.

- 2) Boolean Expression is an expression in Boolean algebra that represents the logic circuit.

- 3) Truth Table provides a concise list that shows all the output states for each possible combination of inputs

|            |   |   | 0 10110 |

|------------|---|---|---------|

| Α          | В | С | Q       |

| <b>A</b> 0 | 0 | 0 | 0       |

| 0          | 0 | 1 | 1       |

| 0          | 1 | 0 | 0       |

| 0          | 1 | 1 | 0       |

| 1          | 0 | 0 | 0       |

| 1          | 0 | 1 | 0       |

| 1          | 1 | 0 | 0       |

| 1          | 1 | 1 | 0       |

|            |   |   |         |

```

process (A, B, C)

begin

if( A = '0' and B = '0' and C = '1') then

Q <= '1';

else

Q <= '0';

end if;

end process;</pre>

```

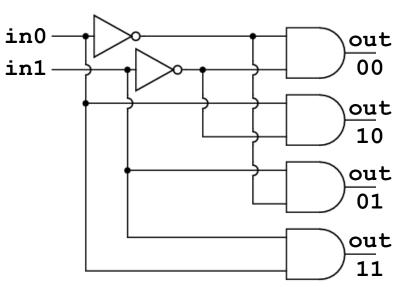

## Comb. Circuit Example: Decoder (1/2)

A decoder is designed to converts binary information from the n inputs to a maximum of  $2^n$  unique outputs.

```

use IEEE.STD LOGIC 1164.ALL;

entity decoder ex is

port (in0, in1: in std logic;

out00, out01, out10, out11: out std logic);

end decoder ex;

architecture decoder ex arch of decoder ex is

begin

process (in0, in1)

begin

if in0 = '0' and in1 = '0' then

out00 <= '1';

else

out00

out00 <= '0';

end if;

```

library IEEE;

|         |         |           | _         |           |           |

|---------|---------|-----------|-----------|-----------|-----------|

| in<br>O | in<br>1 | out<br>00 | out<br>01 | out<br>10 | out<br>11 |

| 0       | 0       | 1         | 0         | 0         | 0         |

| 0       | 1       | 0         | 1         | 0         | 0         |

| 1       | 0       | 0         | 0         | 1         | 0         |

| 1       | 1       | 0         | 0         | 0         | 1         |

## Comb. Circuit Example: Decoder (2/2)

```

<u>(cont'd)</u>

if in0 = '0' and in1 = '1' then

out01 <= '1';

out01

else

out01 <= '0';

end if;

if in0 = '1' and in1 = '0' then

out10 <= '1';

out10

else

out10 <= '0';

end if;

if in0 = '1' and in1 = '1' then

out11 <= '1';

out11

else

out11 <= '0';

end if;

end process;

end decoder ex arch;

```

| in<br>0 | in<br>1 | out<br>00 | out<br>01 | out<br>10 | out<br>11 |

|---------|---------|-----------|-----------|-----------|-----------|

| 0       | 0       | 1         | 0         | 0         | 0         |

| 0       | 1       | 0         | 1         | 0         | 0         |

| ~       | 0       | 0         | 0         | 1         | 0         |

| 1       | 1       | 0         | 0         | 0         | 1         |

#### Class Exercise 3.1

Re-implement the 2-to-4 decoder by referring the

provided schematic diagram:

```

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

entity decoder_ex is

port(in0,in1: in std_logic;

out00,out01,out10,out11:

out std_logic);

end decoder_ex;

architecture decoder_ex_arch of decoder_ex is

begin

```

| in<br>0 | in<br>1 | out<br>00 | out<br>01 | out<br>10 | out<br>11 |

|---------|---------|-----------|-----------|-----------|-----------|

| 0       | 0       | 1         | 0         | 0         | 0         |

| 0       | 1       | 0         | 1         | 0         | 0         |

| 1       | 0       | 0         | 0         | 1         | 0         |

| 1       | 1       | 0         | 0         | 0         | 1         |

end decoder ex arch;

### Comb. Circuit Example: Multiplexer

A multiplexer is designed to switch one of several input lines through to a single common output line.

```

library IEEE;

use IEEE.STD LOGIC 1164.ALL;

entity mux ex is

port (in1, in2, sel: in std logic;

out1: out std logic);

end mux ex;

architecture mux ex arch of mux ex is

begin

process (in1, in2, sel)

begin

if sel = '0' then

out1 <= in1; -- select in1</pre>

else

out1 <= in2; -- select in2</pre>

end if;

end process;

end mux ex arch;

```

| sel | in1 | in2 | out1 |

|-----|-----|-----|------|

|     | 0   | 0   | 0    |

| 0   | 0   | 1   | 0    |

| 0   | 1   | 0   | 1    |

|     | 1   | 1   | 1    |

| 1   | 0   | 0   | 0    |

|     | 0   | 1   | 1    |

|     | 1   | 0   | 0    |

|     | 1   | 1   | 1    |

#### Class Exercise 3.2

Specify the I/O signals in the schematic diagram:

```

library IEEE;

use IEEE.STD LOGIC 1164.ALL;

entity mux ex is

port (in1, in2, sel: in std logic;

out1: out std logic);

end mux ex;

MUX

architecture mux ex arch of mux ex is

begin

process (in1, in2, sel)

begin

if sel = '0' then

out1 <= in1; -- select in1</pre>

2

else

out1 <= in2; -- select in2</pre>

end if;

end process;

end mux ex arch;

```

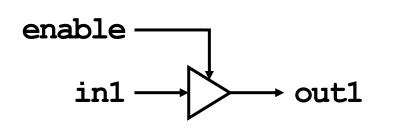

#### **Recall: Tri-state Buffer**

| in1 | enable | out1 |

|-----|--------|------|

| 0   | 0      | Z    |

| 1   | 0      | Z    |

| 0   | 1      | 0    |

| 1   | 1      | 1    |

```

library IEEE;

use IEEE.STD LOGIC 1164.ALL;

entity tri ex is

port (in1, enable: in std logic;

out1: out std logic);

end tri ex;

architecture tri ex arch of tri ex is

begin

out1 <= in1 when enable = '1' else 'Z';

end tri ex arch;

```

#### **Outline**

- Combinational Circuit: no memory

- Outputs depend on the *present* inputs only.

- Rule: Use either concurrent or sequential statements.

- Sequential Circuit: has memory

- Outputs depend on present inputs and previous outputs.

- Rule: MUST use sequential statements (i.e., process).

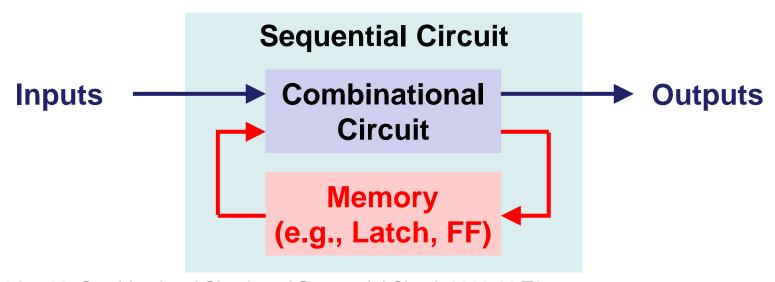

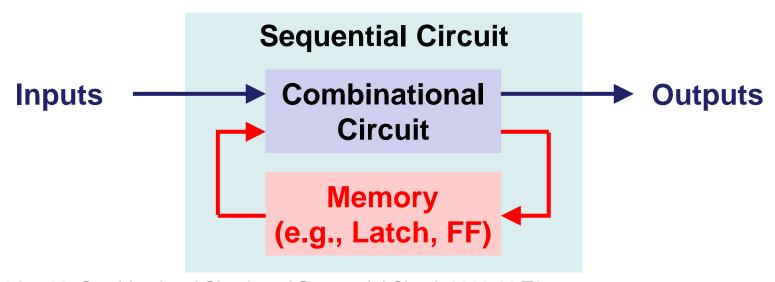

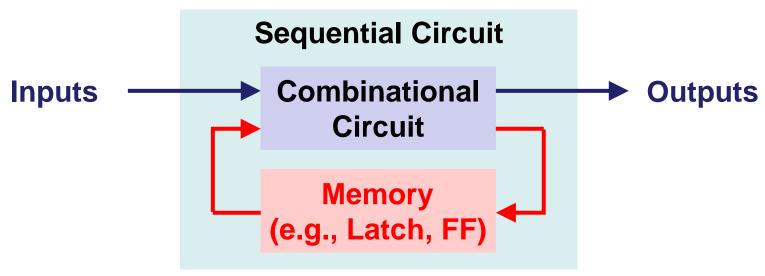

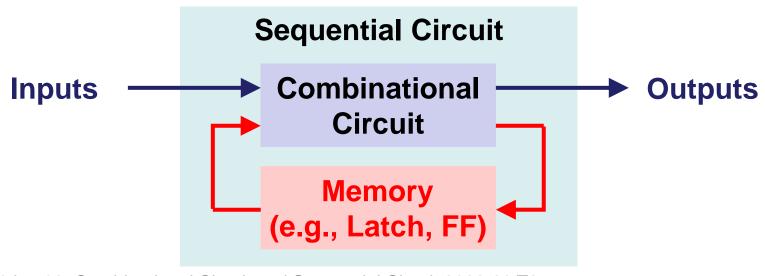

## **Sequential Circuit**

- Sequential Circuit: has memory

- Outputs depend on present inputs and previous outputs.

- The previous output(s) are kept in the memory device(s) and treated as the present state.

- Two most common memory devices: Latch and Flip-flop (FF), both can hold one bit of data (i.e., either low or high).

- Rule: You MUST build a sequential circuit with <u>only</u>

sequential statements (i.e., statements inside process).

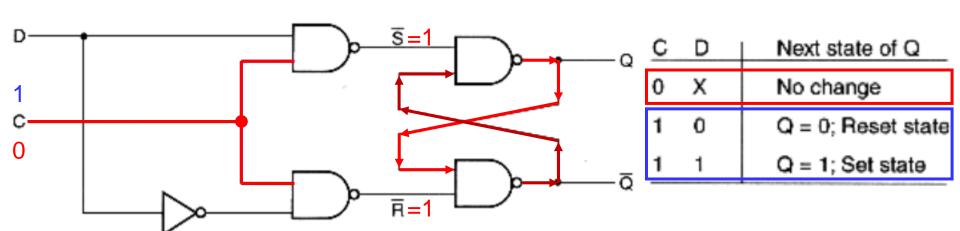

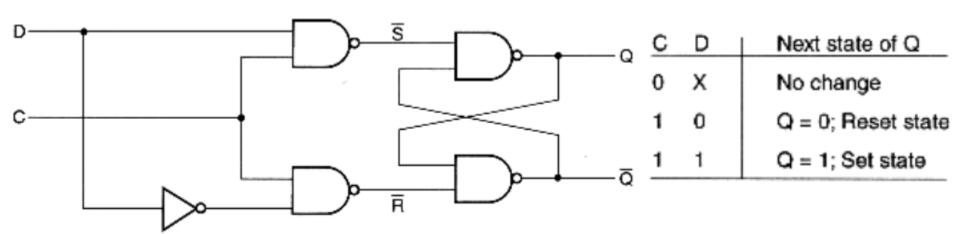

#### **Memory Device: Latch**

- Latch has no CLOCK signal.

- It changes the output in accordance with the enable signal.

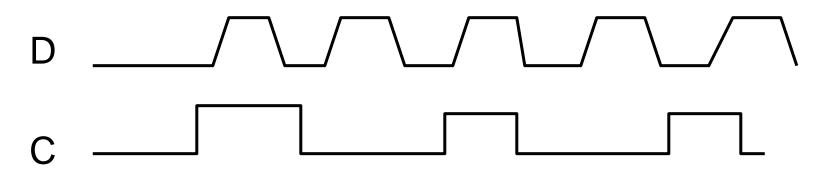

- Case Study: D Latch

- When enable signal C is high, the output Q follows input D.

- That is why D latch is also called as transparent latch: When enable line C is asserted, the latch is said to be transparent.

- When C falls, the last state of D is held (i.e., has memory)!

#### D Latch in VHDL

15 end latch ex arch;

```

1 library IEEE; -- (ok vivado 2014.4)

2 use IEEE.STD LOGIC 1164.ALL;

3 entity latch ex is

4 port (C, D: in std logic;

Q: out std logic);

6 end latch ex;

7 architecture latch ex arch of latch ex is

begin

process (C, D) -- sensitivity list

begin

10

Next state of Q

if (C = '1') then

Х

No change

12

Q \leftarrow D;

end if;

13

Q = 0; Reset state

-- no change (memory

Q = 1; Set state

end process;

14

```

https://www.edgefx.in/digital-electronics-latches-and-flip-flops/

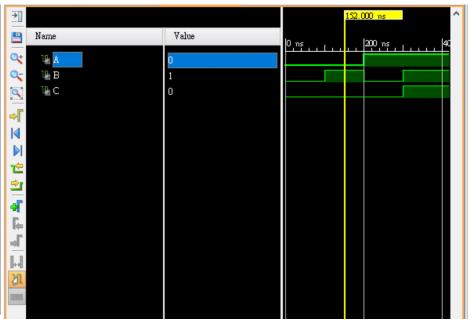

#### Class Exercise 3.3

Given a D latch, draw Q in the following figure:

Q

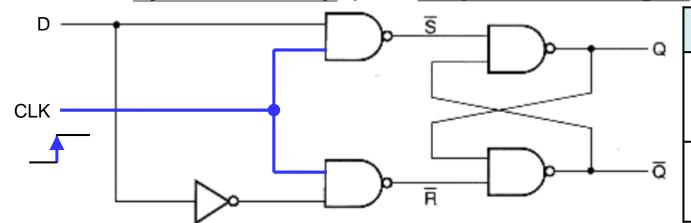

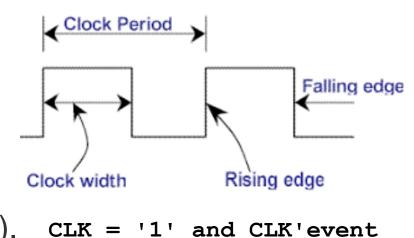

## Memory Device: Flip-flop (FF)

- Flip-flop has a clock signal (i.e., CLK).

- It changes the output at clock edges.

- Positive-Edge-Triggered: At every low to high of CLOCK.

- Negative-Edge-Triggered: At every high to low of CLOCK.

- Whenever the clock rises, the output Q follows input D.

- Otherwise, the last state of D is held (i.e., has memory)!

- The held value can be reset <u>asynchronously</u> (i.e., <u>anytime</u>) or synchronously (i.e., only at clock edges).

| CLK            | D | $Q_{next}$ |

|----------------|---|------------|

| ricina         | 0 | 0          |

| rising         | 1 | 1          |

| non-<br>rising | X | Q          |

## D Flip-flop with Async. Reset in VHDL

```

RESET

1 library IEEE;

2 use IEEE.STD LOGIC 1164.ALL;

Positive-

3 entity DFF ASYNC is

Edge-

4 port (D, CLK, RESET: in std logic;

Triggered

Q: out std logic);

6 end dff async;

architecture DFF ASYNC ARCH of DFF ASYNC is

begin

process (CLK, RESET) -- sensitivity list

begin

10

if (RESET = '1') then

11

O <= '0'; -- Reset Q anytime

12

Positive-

elsif CLK = '1' and CLK'event then

13

← edge-

Q <= D; -- Q follows input D

14

triggered

end if;

15

-- no change (so has memory)

end process;

17 end DFF ASYNC ARCH;

```

#### **Attribute**

- An attribute provides information about items such as entities, architecture, signals, and types.

- The syntax is an apostrophe (') and the attribute name.

- There are several useful predefined value, signal, and range attributes (see <u>VHDL Predefined Attributes</u>).

- An important signal attribute is the 'event.

- This attribute yields a Boolean value of TRUE if an event has just occurred on the signal.

- It is used primarily to determine if a clock has transitioned (i.e., either low-to-high or high-to-low).

## D Flip-flop with Sync. Reset in VHDL

```

RESET

1 library IEEE;

2 use IEEE.STD LOGIC 1164.ALL;

Positive-

3 entity DFF SYNC is

Edge-

4 port (D, CLK, RESET: in std logic;

Triggered

Q: out std logic);

end DFF SYNC;

architecture DFF SYNC ARCH of DFF SYNC is begin

process (CLK) ← Shall we put RESET in the sensitivity list?

8

begin

if CLK = '1' and CLK'event then

10

if (RESET = '1') then

11

0 <= '0'; -- Reset Q at edges</pre>

12

Positive-

← edge-

13

else

triggered

14

Q <= D; -- Q follows input D

15

end if;

end if;

16

-- no change (so has memory)

end process;

end DFF SYNC ARCH;

```

## Async. Reset vs. Sync. Reset

- The order of the statements <u>inside the process</u> determines <u>asynchronous reset</u> or <u>synchronous reset</u>.

- Asynchronous Reset (check RESET first!)

```

if (RESET = '1') then

Q <= '0'; -- Reset Q anytime

elsif CLK = '1' and CLK'event then

Q <= D; -- Q follows input D

end if;

```

– Synchronous Reset (check CLK first!)

```

if CLK = '1' and CLK'event then

if (RESET = '1') then

2 <= '0'; -- Reset Q at edges

else

2 <= D; -- Q follows input D

end if;

end if;</pre>

```

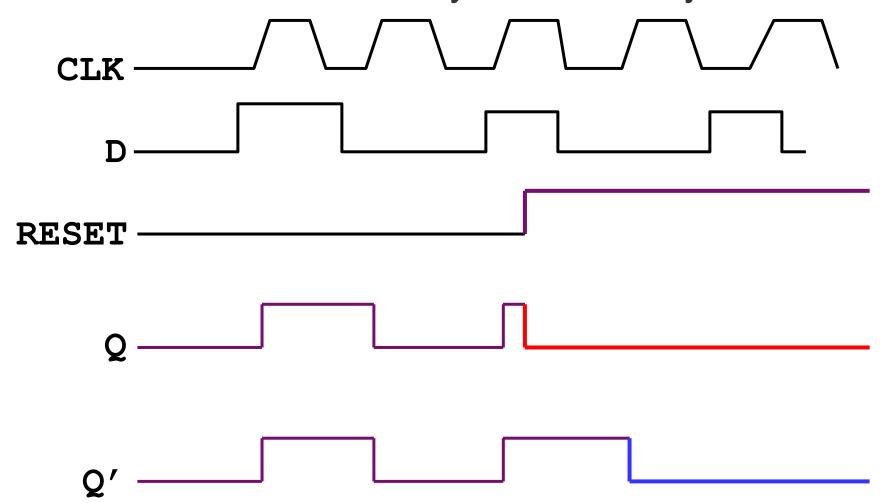

#### Class Exercise 3.4

Given a pos-edge-triggered D FF, determine whether Q and Q' are based on async. reset or sync. reset:

## Latch vs. Flip-flop (FF)

- Latch and Flip-flop (FF) are both typical memory devices which can store one bit of data.

- Latch has no clock signal and is level-triggered.

- The output of a latch can be changed only when the level of enable signal C is high.

- FF has a clock signal and is edge-triggered.

- The output of an FF can only be changed whenever the clock signal goes from low to high and high to low (i.e., clock edges).

- FF can be found in a wide range of sequential circuits where time plays an essential role.

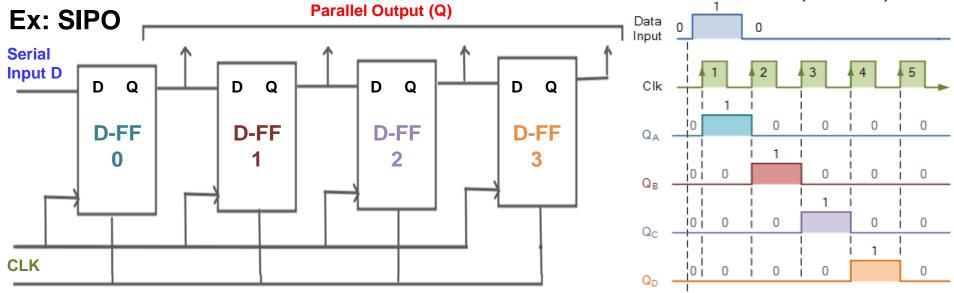

## Seq. Circuit Example: Shift Register

- A register is a device that can be composed of a group of FFs to store multiple bits of data.

- A shift register allows the stored data being moved from one FF to another.

- There are basically **four** types: ① Serial-In-Serial-Out

(SISO), ② Serial-In-Parallel-Out (SIPO), ③ Parallel-In-Serial-Out (PISO). and ④ Parallel-In-Parallel-Out (PIPO).

#### SIPO Shift Register in VHDL

```

entity SIPO ASYNC is

port (D, CLK, RST : IN STD LOGIC;

Q: OUT STD LOGIC VECTOR(3 downto 0);

end SIPO ASYNC;

architecture SIPO ASYNC ARCH of SIPO ASYNC is

component <u>DFF ASYNC</u> is

port(D, clk, reset : in STD LOGIC;

Q : out STD LOGIC );

end component;

signal dout : STD LOGIC VECTOR(3 downto 0); ← necessary?

begin

DFF0: DFF ASYNC port map(D, CLK, RST, dout(0));

DFF1: DFF ASYNC port map(dout(0), CLK, RST, dout(1));

DFF2: DFF ASYNC port map(dout(1), CLK, RST, dout(2));

DFF3: DFF ASYNC port map(dout(2), CLK, RST, dout(3));

Q <= dout;</pre>

end SIPO ASYNC ARCH;

```

#### Recall: Modes of I/O Pins

Modes of I/O pin must be <u>explicitly specified</u> in port of entity declaration:

#### Example:

```

entity eqcomp4 is

port (a, b: in std_logic_vector(3 downto 0);

equals: out std_logic);

end eqcomp4;

```

- There are 4 available modes of I/O pins:

- 1) in: Data flows in only

- 2) out: Data flows out only (cannot be read back by the entity)

- 3) inout: Data flows bi-directionally (i.e., in or out)

- 4) buffer: Similar to out but it can be read back by the entity

## **Summary**

- Combinational Circuit: no memory

- Outputs depend on the *present* inputs only.

- Rule: Use either concurrent or sequential statements.

- Sequential Circuit: has memory

- Outputs depend on present inputs and previous outputs.

- Rule: MUST use sequential statements (i.e., process).